QR Code

Prodotti

Contattaci

Telefono

Fax

+86-579-87223657

E-mail

Indirizzo

Wangda Road, Ziyang Street, contea di Wuyi, città di Jinhua, provincia di Zhejiang, Cina

Nel mondo dei semiconduttori a banda larga (WBG), se il processo di produzione avanzato è l'"anima", il suscettore di grafite è la "spina dorsale" e il suo rivestimento superficiale è la "pelle" critica. Questo rivestimento, in genere spesso solo decine di micron, determina la durata dei costosi materiali di consumo in grafite in ambienti termochimici difficili. Ancora più importante, influisce direttamente sulla purezza e sulla resa della crescita epitassiale.

Attualmente, due principali soluzioni di rivestimento CVD (Chemical Vapour Deposition) dominano il settore:Rivestimento in carburo di silicio (SiC).ERivestimento in carburo di tantalio (TaC).. Sebbene entrambi svolgano ruoli essenziali, i loro limiti fisici creano una chiara divergenza di fronte alle esigenze sempre più rigorose della fabbricazione di nuova generazione.

1. Rivestimento SiC CVD: lo standard di settore per i nodi maturi

In quanto punto di riferimento globale per la lavorazione dei semiconduttori, il rivestimento CVD SiC è la soluzione "go-to" per i suscettori GaN MOCVD e le apparecchiature epitassiali (Epi) SiC standard. I suoi vantaggi principali includono:

Sigillatura ermetica superiore: il rivestimento SiC ad alta densità sigilla efficacemente i micropori della superficie di grafite, creando una robusta barriera fisica che impedisce alla polvere di carbonio e alle impurità del substrato di degassare alle alte temperature.

Stabilità del campo termico: con un coefficiente di espansione termica (CTE) strettamente corrispondente ai substrati di grafite, i rivestimenti SiC rimangono stabili e privi di crepe entro la finestra di temperatura epitassiale standard compresa tra 1000°C e 1600°C.

Efficienza in termini di costi: per la maggior parte della produzione di dispositivi di potenza tradizionali, il rivestimento SiC rimane il "punto debole" in cui le prestazioni incontrano il rapporto costo-efficacia.

Con lo spostamento del settore verso wafer SiC da 8 pollici, la crescita dei cristalli PVT (Physical Vapor Transport) richiede ambienti ancora più estremi. Quando le temperature superano la soglia critica di 2000°C, i rivestimenti tradizionali incontrano un limite prestazionale. È qui che il rivestimento CVD TaC diventa un punto di svolta:

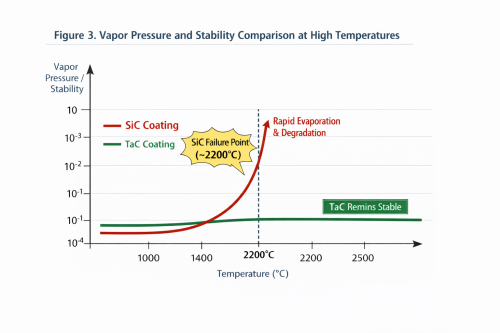

Stabilità termodinamica senza pari: il carburo di tantalio (TaC) vanta uno sbalorditivo punto di fusione di 3880°C. Secondo una ricerca pubblicata sul Journal of Crystal Growth, i rivestimenti SiC subiscono una “evaporazione incongruente” sopra i 2200°C, dove il silicio sublima più velocemente del carbonio, portando al degrado strutturale e alla contaminazione delle particelle. Al contrario, la pressione di vapore di TaC è compresa tra 3 e 4ordini di grandezza inferiori al SiC, mantenendo un campo termico incontaminato per la crescita dei cristalli.

Inerzia chimica superiore: nelle atmosfere riducenti che coinvolgono H₂ (idrogeno) e NH₃ (ammoniaca), TaC mostra un'eccezionale resistenza chimica. Esperimenti di scienza dei materiali indicano che il tasso di perdita di massa del TaC nell'idrogeno ad alta temperatura è significativamente inferiore a quello del SiC, il che è vitale per ridurre le dislocazioni della filettatura e migliorare la qualità dell'interfaccia negli strati epitassiali.

3. Confronto chiave: come scegliere in base alla finestra del processo

Scegliere tra questi due non riguarda la semplice sostituzione, ma l'allineamento preciso con la "finestra del processo".

|

Metrica delle prestazioni |

Rivestimento SiC CVD |

Rivestimento TaC CVD |

Significato tecnico |

|

Punto di fusione |

~2730°C (sublimazione) |

3880°C |

Integrità strutturale in condizioni di caldo estremo |

|

Temp. massima consigliata |

2000°C - 2100°C |

2400°C+ |

Consente la crescita dei cristalli su larga scala |

|

Stabilità chimica |

Buono (vulnerabile all'H₂ a temperature elevate) |

Eccellente (Inerte) |

Determina la purezza dell'ambiente di processo |

|

Pressione di vapore (2200°C) |

Alto (rischio di perdita di silicio) |

Ultra-basso |

Controlla i difetti di "inclusione di carbonio". |

|

Applicazioni principali |

Epitassia GaN/SiC, suscettori LED |

Crescita SiC PVT, Epi ad alta tensione |

Allineamento della catena del valore |

L'ottimizzazione della resa non è un singolo passo avanti, bensì il risultato di un preciso abbinamento dei materiali. Se stai lottando con le "inclusioni di carbonio" nella crescita dei cristalli SiC o stai cercando di ridurre drasticamente il costo dei materiali di consumo (CoC) prolungando la vita delle parti in ambienti corrosivi, il passaggio da SiC a TaC è spesso la chiave per sbloccare la situazione.

In qualità di sviluppatore dedicato di materiali di rivestimento avanzati per semiconduttori, VeTek Semiconductor ha padroneggiato entrambi i percorsi tecnologici CVD SiC e TaC. La nostra esperienza dimostra che non esiste il materiale "migliore", ma solo la soluzione più stabile per uno specifico regime di temperatura e pressione. Attraverso il controllo preciso dell'uniformità della deposizione, consentiamo ai nostri clienti di ampliare i limiti della resa dei wafer nell'era dell'espansione da 8 pollici.

Autore:Sera Lee

Riferimenti:

[1] "Pressione di vapore ed evaporazione di SiC e TaC in ambienti ad alta temperatura", Journal of Crystal Growth.

[2] "Stabilità chimica dei carburi metallici refrattari in atmosfere riducenti", Chimica e fisica dei materiali.

[3] "Controllo dei difetti nella crescita di cristalli singoli SiC di grandi dimensioni utilizzando componenti rivestiti con TaC", Forum di scienza dei materiali.

+86-579-87223657

Wangda Road, Ziyang Street, contea di Wuyi, città di Jinhua, provincia di Zhejiang, Cina

Copyright © 2024 WuYi TianYao Advanced Material Tech.Co.,Ltd. Tutti i diritti riservati.

Links | Sitemap | RSS | XML | politica sulla riservatezza |